AMD EPYC 9005 シリーズプロセッサ

第5世代 AMD EPYC プロセッサーは、“Zen 5”コアと“Zen 5c”コアを採用しています。この2つのコアの主な違いは、CPUコアあたりのL3キャッシュ容量にあります。Zen 5は1コアあたり4MBのL3キャッシュを備え、Zen 5cは1コアあたり2MBとなっています。

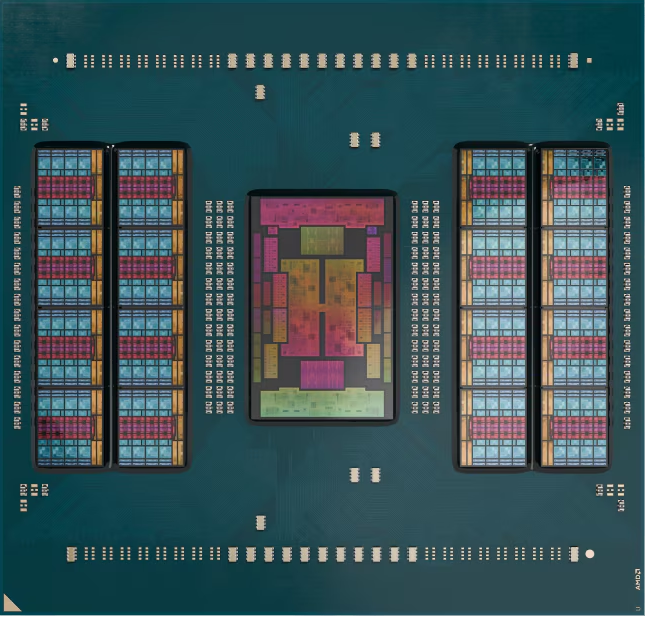

また、EPYCシリーズの特徴であるチップレット構造は第5世代でも継承されており、Zen 5コアを採用したモデルでは最大128コア、Zen 5cコアを採用したモデルでは最大192コアを搭載しています。さらに、Zen 5は4nmプロセス、Zen 5cは3nmプロセスで製造されており、最新のプロセス技術を活用することで、ブーストクロック時には最大5GHzに達するSKUも存在し、高い性能を発揮します。

メモリ仕様については、第4世代 EPYC(EPYC 9004シリーズ)と同様に最大12チャンネルのDDR5メモリ(最大DDR5-6400)に対応しています。さらに、PCI Express 5.0に対応し、2ソケット構成の場合は最大160レーンのPCI Express 5.0をサポートしています。また、第5世代 EPYCからは新たにCXL 2.0にも対応しています。

第5世代 EPYCは、第4世代で採用された「SP5ソケット」を引き続き使用しており、BIOSやファームウェアのアップデートが必要になる場合があるものの、基本的には同じマザーボードやメモリモジュールを利用可能です。そのため、多くのサーバーモデルが第4世代と第5世代の両方に対応しています。

AMD EPYC™ 9005シリーズは、次世代データセンター向けに設計された高性能プロセッサで、革新的なテクノロジーとスケーラビリティを実現します。このプロセッサシリーズは、最大128コア(Zen 4cアーキテクチャ)を搭載し、マルチスレッド処理において卓越したパフォーマンスを発揮します。以下に、主な特徴をまとめました。

主な特徴

-

高いコア数とスレッド数:

最大192コア/384スレッドをサポートし、高密度仮想化やAI/MLワークロードに最適。

-

エネルギー効率の向上:

最新の5nmプロセス技術を採用し、パフォーマンスと電力効率を最適化。より持続可能なデータセンター運用が可能。

-

広範なメモリサポート:

DDR5メモリおよびPCIe 5.0に対応し、高速かつ大容量のデータアクセスを実現。

-

セキュリティ機能の強化:

AMD Infinity Guardを搭載し、セキュアブートやメモリ暗号化などの最新セキュリティ技術を提供。

-

柔軟な拡張性:

マルチソケット構成に対応し、最大限のスケーラビリティを実現。ハイパフォーマンスコンピューティング(HPC)からクラウド、エッジコンピューティングまで、幅広いユースケースに対応可能。

-

先進的なI/O帯域幅:

最大128レーンのPCIe 5.0をサポートし、最新のストレージやネットワーキングソリューションに対応。

利用シーン

- クラウドおよび仮想化: 大規模なクラウド環境での効率的な仮想化を実現。

- AI/ML: AIトレーニングや推論タスクにおける高スループット。

- HPC: 科学技術計算やシミュレーションなどの高性能コンピューティングタスクに最適。

- エンタープライズ: データベースやERP、分析などの企業向けワークロードの高速化。