| インテル社が主催する開発者向け会議「Intel

Developer Forum (IDF) fall 2006」については、既に、詳細なレポートがWEBニュースとして、公開されており、その中で、この会議で紹介された技術や最新のロードマップなどが紹介されています。(キーノートの詳細などもWEBで配信、その他、様々な解説記事がWEB上にあります)

今回のIDFでの基調講演では、「テラ・スケールコンピューティング」について、多くの発表がありました。これらは、製品発表ではなく、インテルの行っている「Intel®

Tera-scale Computing Research Program」の内容についての発表となっています。

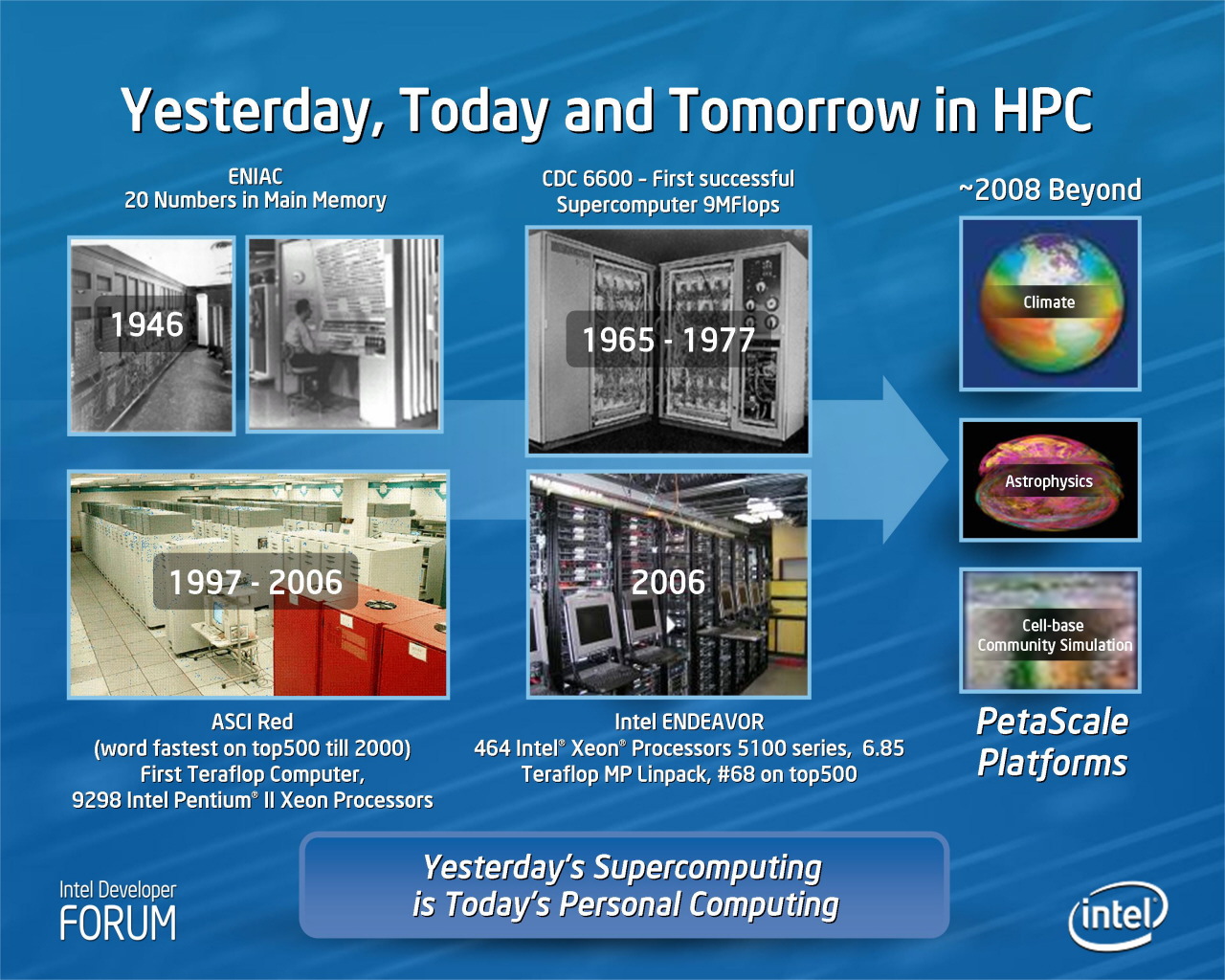

今回のIDFでは、この「テラ・スケールコンピューティング」とその技術をベースとする「ペタFLOPS」のピーク性能を持つ計算機システムに関する説明がありました。現在、欧米や日本でも、「ペタFLOPS」級のコンピュータシステムの開発

計画が議論されていますが、現実的には、マイクロプロセッサ自身が、「テラFLOPS」の演算性能と「テラBytes/s」のバンド幅、そして、「テラBytes/s」のIO性能を必要としています。現在のマイクロプロセッサを数万〜数十万個接続することは、実際には現実的ではないため、マイクロプロセッサ自身の大きな進化が必要となっています。

|

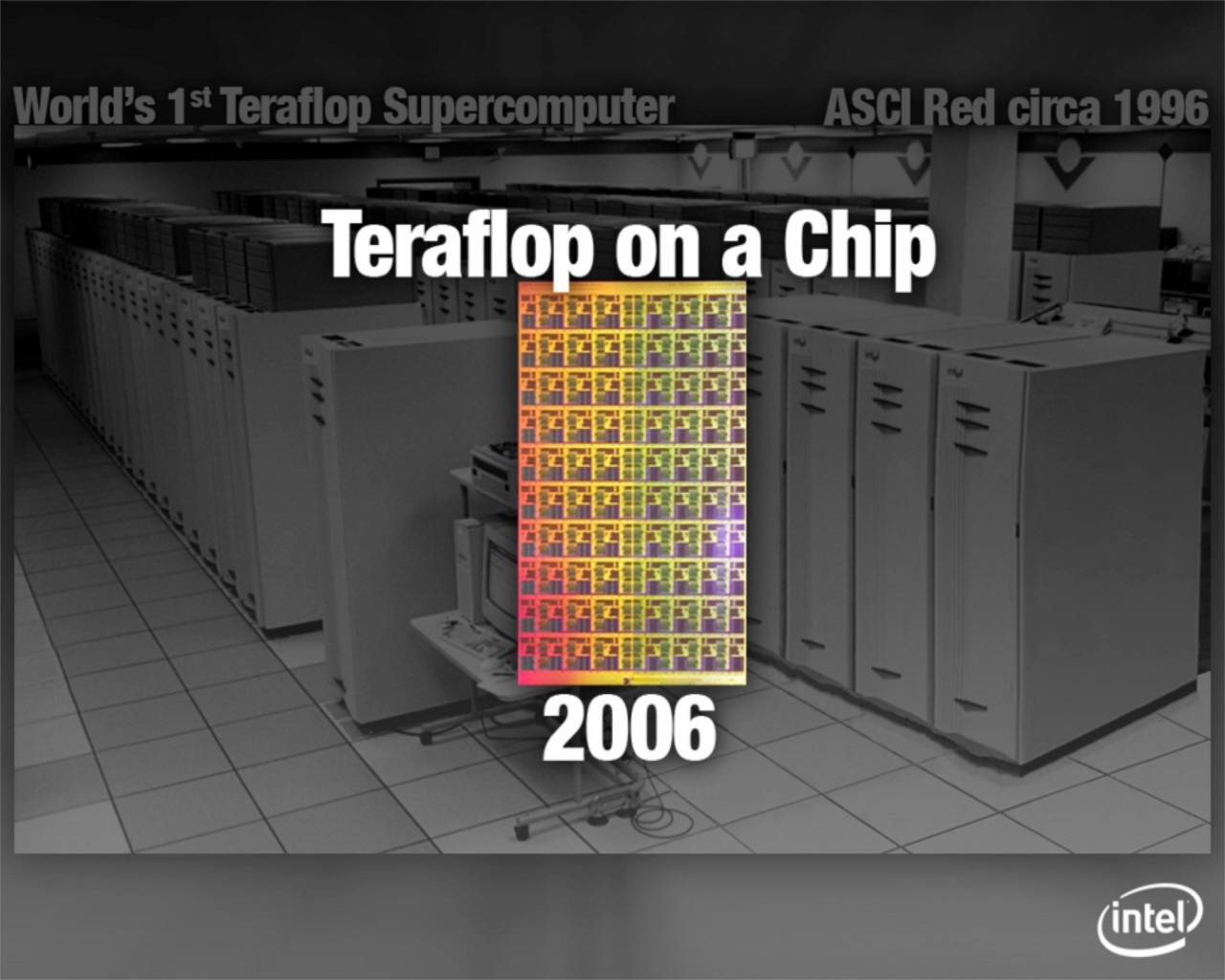

テラFLOPS、すなわち毎秒 1 兆回以上の浮動小数点演算を行う計算機システムは、1996年にインテルが、7264 個の

Pentium® Pro プロセッサーを搭載したスーパーコンピューターを開発し、1.06 テラフロップスの記録 (Linpackベンチマーク)

が最初のシステムとなります。このシステムは、57 台のキャビネットで構成され、その後、9200 個のプロセッサ、84

台のキャビネットに拡張され、最終的な理論最大性能は、1.8 テラフロップとなりました。 |

|

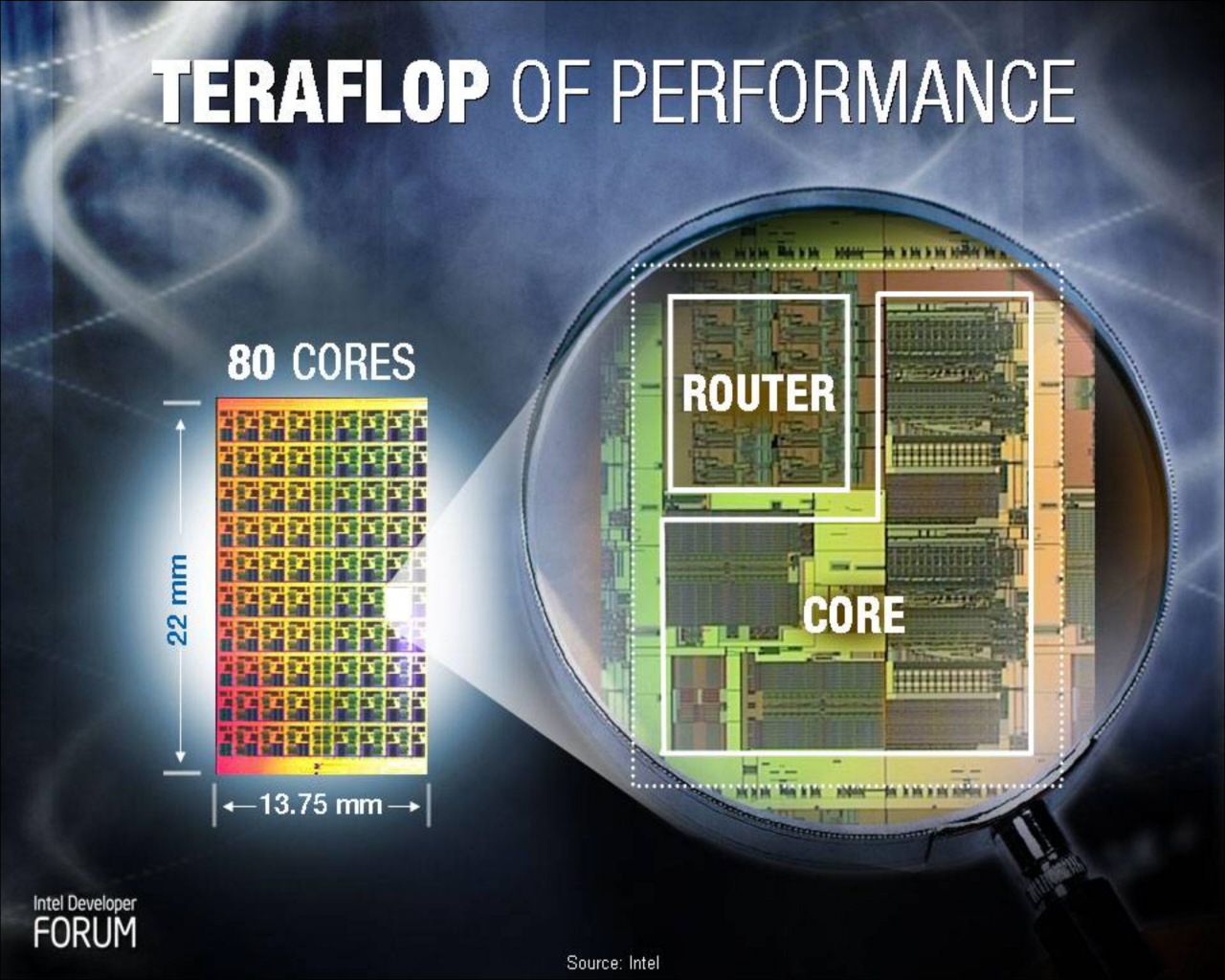

IDFの中で,80個のCPUコアを1チップ上に集積したマイクロプロセサの試作品が初公開されました。

面積が22mm×13.75mmのダイに,10個×8個のCPUコアを集積している。各CPUコアは,スイッチ回路を備えています。試作したマイクロプロセサの演算性能は,1個で1TFLOPSと1996年時点での世界最速のスーパーコンピュータ並みの性能となっています。コア数の他にも,メモリと各CPUコアが1対1で接続され,それぞれ256Mバイト/秒のメモリ帯域幅を持つなど,従来にない3次元的なアーキテクチャを採用しているのが特徴となっています。

このマイクロプロセッサは、1Watts当たりの性能が100GFLOPS程度となることが説明されています。また、このマイクロプロセッサでのメモリ接続とインターコネクトのための新しい技術も紹介されています。

「Tera-scale Computing

」では、扱うデータ量やパフォーマンス」をギガ単位からテラ単位で処理できるような要素技術(HWとSW)が、ここでは紹介されていました。これらの技術を利用することで、「ペタ・スケール」へと向かう「ハイ・パフォーマンス・コンピューティング」のニーズに応えることも検討さています。

実際、「ハイ・パフォーマンス・コンピューティング」で要求される「ペタFLOPS」級のシステムでは、電力効率、システム全体の信頼性、アプリケーションの並列化など、様々な問題を解決する必要があります。その基盤として、インテルはこのような非常に多くのコアを持つマイクロプロセッサを研究していることをアピールしています。 |

|

|

|

マイクロプロセッサ単体の性能は、既に1990年代のスーパーコンピュータの性能を上回っています。このように、将来的にも、より高性能なPCは、現在のスーパーコンピュータの性能を上回ることになります。そんな高性能をPCが必要であるか?という議論もありますが、PCの性能向上は、継続的に続き、また、その利用方法やアプリケーションも変わってきています。その意味では、PC自身の高性能化は、今後も継続することになると思われます。 |

技術セッションでも、幾つかのセッションでも、「Tera-scale Computing 」の説明がありました。

- TCRS001 The Future of Computing: Tera-scale Computing Research

Overview

- TCRS002 Hundreds of Cores: Scaling to Tera-scale Architectures

これらの技術セッションの話題は、現在のマイクロプロセッサをベースに数千、数万コアを接続して、並列計算機を開発することの問題点も示しながら、どのように「Tera-scale

Computing

」を実現するかを示しています。直接、現在のコンピュータシステムの技術革新に寄与するかは、わかりませんが、現状の問題点とその克服に関する意見として参考にはなります。

ただ、同時にHPCのトピックスとして、以下のようなパネルディスカッションもあり、実際には、こちらの説明の方がより現実的な問題を明確にしています。

- HPCP001 The Great Debate: The Rocky Road to PetaFLOP Computing

|