# Intel Developer Forum (IDF) Fall 2006 特別レポート

「米 Intel の CTO(最高技術責任者)が語る HPC の将来」

スケーラブルシステムズ株式会社

## ハイパフォーマンス|パーソナルクラスタ

| 1. | はじめに                        | . 2 |

|----|-----------------------------|-----|

|    |                             |     |

| 2. | '今日の'スーパーコンピュータ             | , 3 |

| 3. | ' ペタ FLOPS 級 'スーパーコンピュータの構築 | . 5 |

| 4. | おわりに                        | . 8 |

スケーラブルシステム株式会社では、IT技術とHPCシステムに関する様々な調査レポートを発行しています。

ご購入の際は(Tel:03-5875-4718 E-mail:biz@sstc.co.jp )までお問い合わせ下さい。

社名、製品名などは、一般に各社の商標または登録商標です。

Copyright Scalable Systems Co., Ltd., 2006. Unauthorized use is strictly forbidden. 無断での引用、転載を禁じます。

2006.10.10

### Intel Developer Forum (IDF) Fall 2006 特別レポート

「米 Intel の CTO(最高技術責任者)が語る HPC の将来」

#### 1. はじめに

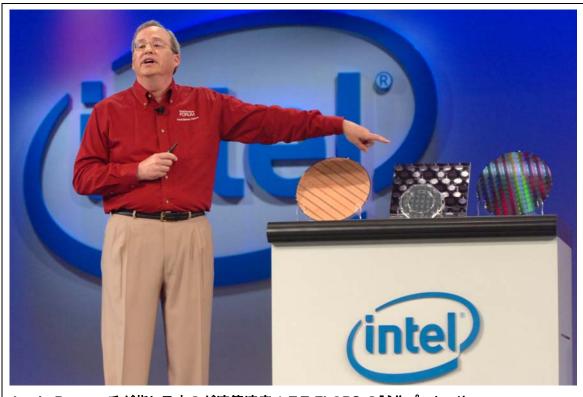

インテル社が主催する開発者向け会議「Intel Developer Forum (IDF) fall 2006」の最終日に米 Intel の Stephen Pawlowski 氏(シニアフェロー, デジタル・エンタープライズ・グループ CTO, ジェネラル・マネジャ)による HPC に関する基調講演があり、「Aim High / To Petascale... and Beyond」と題した講演がありました。

今回のIDFでは、2006年の春のイベントのような大きなマイクロプロセッサに関する発表はありませんでしたが、初日の Justin Rattner 氏(シニア・フェロー兼最高技術責任者(CTO)兼コーポレート・テクノロジー統括本部長)の講演でも、80 個のコアからなるテラ FLOPS の性能を持つマイクロプロセッサやそのマイクロプロセッサに対してテラバイトのメモリバンド幅を提供するメモリ技術などの講演もあり、大規模なデータセンターやスーパーコンピューティングに関する技術や研究開発の成果などが紹介されています。

Stephen Pawlowski 氏の講演の前には、NASA の Walter Brooks 博士のビデオが紹介されています。このビデオの中で、博士は'…today's supercomputing problem is tomorrow's desktop problem…'ということで、現在の大規模なスーパーコンピュータを必要とする非常に解析困難な問題も、将来はより強力な desktop システムによって、解析可能となるとお話しになっています。

Stephen Pawlowski 氏の講演は、この Walter Brooks 博士の説明を受けて、従来のスーパーコンピュータに匹敵する Desktop システムの紹介と '明日の'スーパーコンピュータについて、インテ

ルとしての課題と挑戦を説明したものとなっています。Stephen Pawlowski 氏は、ご自身でも自分は、ハードウエア・の人間でソフトウエアは、自分の後で講演する Richard B. Wirt 氏(シニアフェロー, ソフトウエア・ソリューショングループ、ジェネラル・マネジャ)が説明すると言っており、実際にどのような形で、、ペタ FLOPS 級 'スーパーコンピュータを構築するかについて説明しています。' ペタ FLOPS 級 'スーパーコンピュータとは、最初のペタ FLOPS のスーパーコンピュータが構築された後で、ピーク性能ではなく、アプリケーションの実効性能として、ペタ FLOPS を超えるスーパーコンピュータのことです。(ロレンス・リバモア国立研究所の Horst Simon 博士の定義) ペタ FLOPS というのは、大きな壁ですが、ピーク性能として、最初にその壁が破られた後でも、アプリケーションレベルで、ペタ FLOPS の壁を打ち破るには、10 ペタ FLOPS を越えるようなスーパーコンピュータが構築可能となることが必要となります。

#### 2. '今日の'スーパーコンピュータ

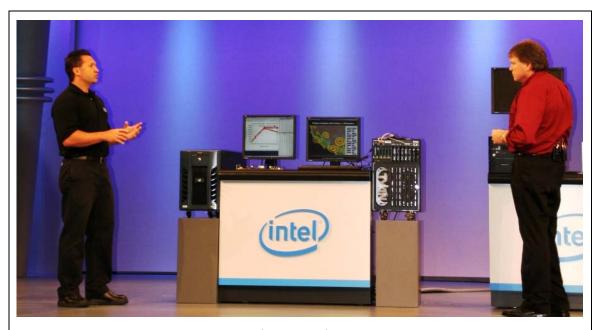

講演の表題にあるペタ FLOPS の話の前に、この講演では '今日の' スーパーコンピュータとして、ユニークな 2 つの製品がステージ上で紹介され、実際のデモが示されています。この '今日の' スーパーコンピュータとして、紹介されたのは、いずれも Desktop(実際には、Deskside に設置することになるとは思いますが)のサイズでありながら、従来のスーパーコンピュータに匹敵する性能と機能を持ったシステムです。

2 台のユニークな'今日の'スーパーコンピュータのデモ

最初に紹介されたのは、Tyan の「パーソナルクラスタ」システム(写真右側)であり、非常にコンパクトな筐体に 40 コアを搭載することを可能としています。このような「パーソナルクラスタ」システムは、大規模な解析を行うことに関して、より高い柔軟性とその適用の可能性を大幅に拡張します。

パーソナルコンピュータが計算機の利用に多くの進化と革新を可能としたように、スーパーコンピュータの新しい可能性を示すものです。デモでは、環境予測のシュミレーションの結果が示されています。このような高度はシュミレーションのこのようなコンパクトな筐体の計算機で十分に可能であることが示されています。

次に紹介されたのは、米 SGI の「共有メモリ並列計算(SMP)」システムです。このシステムは、更にコンパクトな筐体に 48 コアを搭載した共有メモリアーキテクチャのシステムとなります。また、このシステムのデモでは、非常に高いメモリスループットのベンチマーク結果が示されています。共有メモリの大規模なメモリ空間とその巨大なメモリ空間に対するプロセッサ・コアからの高いバンド幅でのアクセスを可能とするこのような SMP システムは、従来は各社が独自のチップセットとインターコネクトなどを開発することが一般的でした。そのため、開発に時間と費用がかかり、また、システムのコストも高いものとなっています。この SGI の SMP システムは、コンパクトな筐体と標準的なハードウエアで作られたものであり、より導入が容易になっています。

#### 3. 'ペタ FLOPS 級 'スーパーコンピュータの構築

このような'今日の'スーパーコンピュータとして、ユニークな製品の紹介の後、インテルが新しく開発したHPC向けの新しいコンパクトなマザーボード S3000PT の紹介の後、いよいよ本題の'ペタ FLOPS 級'スーパーコンピュータの構築の課題と挑戦の話となります。

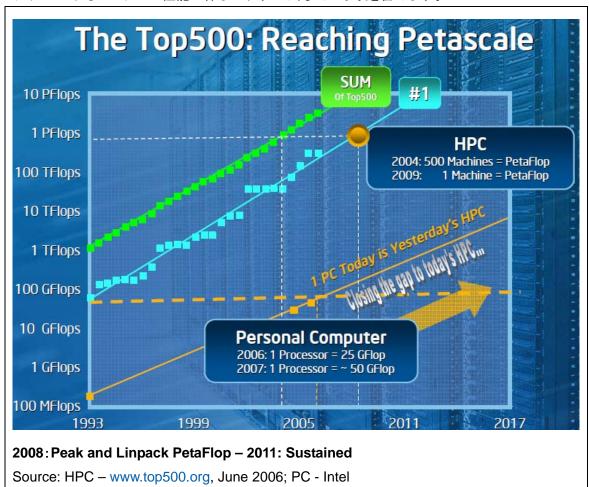

'ペタ FLOPS 級 'スーパーコンピュータを考える時、良く知られた' TOP 500 Supercomputers'のチャートによるシステムの性能の伸びのグラフは、多くの示唆を含みます。

このグラフから予想される'ペタ FLOPS 級 'スーパーコンピュータの実現は、2011 - 2012 年頃になると思われます。この時、'ペタ FLOPS 級 'スーパーコンピュータの実現に必要な技術について、プロセッサ、メモリ、IO について、現在の技術とその技術の発展として、どのような技術が可能か、また、どのように取り組んでいるかの説明が行われています。これらの説明は、IDF 初日の Justin Rattner 氏の講演とかなり重複していますが、Stephen Pawlowski 氏の説明では、より技術的な詳細な考察が行われています。コーポレートの CTO とエンタープライズ・グループの CTO の立場

からの双方の説明を聞くことで、インテルの考える'ペタ FLOPS 級 'スーパーコンピュータの実現

のための要素技術について、より具体的に理解できるようになります。

5

このグラフで示される PC(Personal Computer)の性能向上も、スーパーコンピュータの性能向上を追うように伸びていることが示されています。実際には、ここでいう PC は Desktop で利用可能な処理性能と考えるべきかもしれません。その意味でも、HPC については、PC のパラダイムシフト(Personal Computer から Personal Cluster)を考える必要があるのではないかと思います。

Justin Rattner 氏が指し示すのが演算速度 1 テラ FLOPS の試作プロセッサ

'ペタ FLOPS 級 'スーパーコンピュータの構築には、マルチコアとそのマルチコア技術を最大限に活用することが必須となることは明らかです。今回、インテルが発表した、80 個の浮動小数点演算コアを内蔵する演算速度 1 テラ FLOPS の試作プロセッサは、そのようなマルチコアプロセッサの一つの形を示すものです。プロセッサだけでは、当然、計算は出来ませんが、メモリを 3 次元的にスタックすることで、バンド幅の大幅な向上を図ることも検討されており、今後、コア間の接続方法、メモリの実装など様々な課題を克服することが必要になるとしても、幾つかの基盤技術は、既にインテルとしても対応可能となっていることが示されています。

それと、現在、最も注目されているのが、その電力消費量です。これは、'ペタ FLOPS 級 'スーパーコンピュータの構築だけでなく、大規模なデータセンターの構築でも常に問題になることですが、現在のプロセッサで'ペタ FLOPS 級 'スーパーコンピュータを構築した場合のコストは、そのシステムの運用だけで、膨大な予算を必要とすることになり、非常にクリティカルな問題となります。また、同時に電力管理とシステムの冷却の問題は、トランジスタレベルからファシリティのレベルまで、様々な技術開発が要求されます。

そして、'ペタ FLOPS 級 'スーパーコンピュータにとって、非常に重要となるのが、システムの信頼度です。膨大なリソースが投入される'ペタ FLOPS 級 'スーパーコンピュータでは、それらの構成要素のどこに問題があっても、システム全体への影響があります。これらの問題を解決するために、システム自身には、ある程度の冗長性と再構築と動的な自己診断機能が求められます。このような信頼性の実現についても、システムアーキテクチャから、半導体プロセスの技術、ソフトウエアまで、様々な技術の開発が必要となります。

#### 4. おわりに

この講演の最後に、'ペタ FLOPS 'の次、'エクサ FLOPS'の話があります。誰が、こんな計算機のパワーを必要とするのでしょうか?という疑問に、CRAY 社で、最初の密結合スーパーコンピュータを開発し、今もスーパーコンピュータの開発に関わっている Steve Chen 博士の資料が示されています。'ゼタ FLOPS'まで示されるこのスライドと、2029 年の実現予想でこの講演は締めくられています。

エネルギー効率とマルチコア技術の革新を中核として、様々な部分での技術革新が必要ではありますが、近い将来、'ペタ FLOPS 級 'スーパーコンピュータが実現されることになるでしょう。同時に、'現在 'のスーパーコンピュータは、「パーソナルクラスタ」などとして、より広範囲なユーザのHPC の用途で活用されることになります。

Stephen Pawlowski 氏の講演の後に、Stephen Pawlowski 氏がソフトウエアの話をしています。'ペタFLOPS 級 'スーパーコンピュータの実現には、ソフトウエアの技術革新も必要であることは言うまでもありません。

Richard B. Wirt 氏、David Kuch 氏(OpenMP の父であり、並列コンパイラのパイオニア)、 Stephen Pawlowski 氏