## Barcelona vs Penryn AMDの新しいプロセッサとインテルの製造プロセス 製品とマーケットシェアでの競合

スケーラブルシステムズ株式会社

# この資料について

- ここに掲載した資料は、弊社の調査と見解に基くものであり、資料の中で示されている製品やサービスを提供している各社の公式な見解でも、また、マーケティング戦略に基くものではありません。あくまで、弊社としての意見だということにご注意ください。これらの資料の無断での引用、転載を禁じます。

- 社名、製品名などは、一般に各社の商標または登録商標です。なお、本文中では、特に®、TMマークは明記しておりません。

# この資料について

- マイクロプロセッサへの要求

- インテルコアマイクロアーキテクチャ Core 2

- AMDプロセッサの現状

- インテルとAMDプロセッサの今後

- AMD 「Barcelona」(コード名)

- インテル「Penryn」(コード名)

- ンテル「Nehalem」(コード名)

- ・ 将来動向とまとめ

## マイクロプロセッサへの要求

#### TCO

- 製造コスト

- 消費電力

- チップサイズ

**Going DOWN**

# **Going UP**

スピードと性能

- ・ 高い動作周波数

- 高いメモリバンド幅

- ・マルチコア

スケーラブルシステムズ株

4

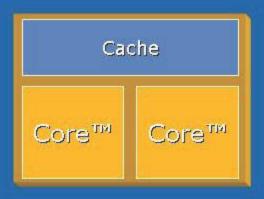

# インテルコアマイクロアーキテクチャ

- インテルの過去最も急速に普及したプロセッサ

- 製品発表後、最初の60日間で500万個を出荷

- 現在までに、1億2000万個のプロセッサを出荷

- 2007年の前半で100万個のクァッドコアプロセッサを出荷(予定)

- 多くのマーケットでのベンチマークで高性能を実証

- モバイル、ディスクトップ、サーバ

- 一部のメモリ性能が性能を左右するアプリケーションでは、AMDはまだ、優位性を示すが、一般には、ほとんどアプリケーションで高性能

- 4ソケットサーバの出荷を予定(2007年第3四半期)

- 製造プロセスでの優位性

- より小さなダイサイズ、より高い動作周波数、低い製造コスト

- より高いFSBバンド幅の実現(1600MHzまたはそれ以上)

- AMDのメモリコントローラのプロセッサ内蔵は、依然として優位性を示すセグメントを持つ

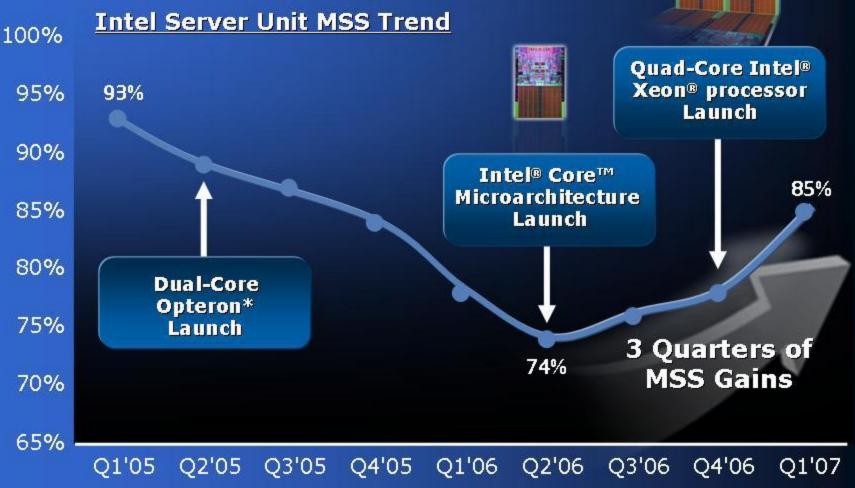

#### Intel Server Momentum with Intel® Core™ Microarchitecture

#### **AMD**

- AMDプロセッサの性能(多くのケースでインテルに劣る)

- プロセッサの動作周波数

- 高い消費電力(65nmプロセッサでも同様に高い)

- 製造プロセスの改善(動作周波数と商品電力の改善)

- HyperTransportとメモリコントローラ内蔵は、AMDの優位性

- 低価格競争

- AMDの成功の尺度は、マーケットシェアの獲得に多くフォーカス

- このマーケットシェアの確保競争は、非常に厳しい経済状況を AMDにもたらす

- ATIの買収コスト

- インテルのクァッドコアプロセッサに対する対応

- (Con)FUSION

- CPUとGPUの統合プランの発表

- 製品ロードマップとプランの発表のみ

- マーケットフォーカスや将来ビジョンの欠如

#### インテル / AMD CPU 2007. 06

#### インテル Core 2 / Xeon

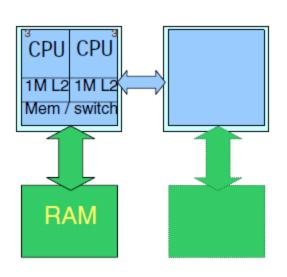

# CPU CPU CPU 4M L2 NORTH BRIDGE RAM

#### **AMD Athron64/Opteron**

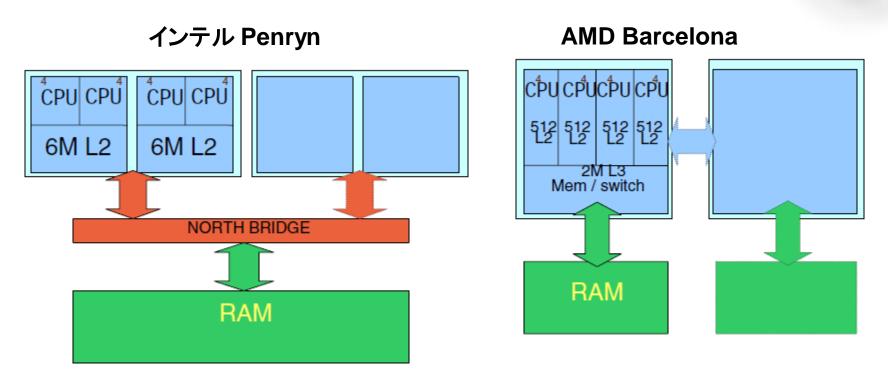

AMDは、メモリコントローラとHyperTransportによる高速、低レイテンシで優位であり、一方インテルは、より大きなキャッシュ、より多くのプロセッサコアの実装とプロセッサ自身の高いピーク性能と高い命令実行で優位

#### Barcelona – AMDの死活問題

- AMDは、再度性能面での優位性を示す必要がある(必 須)

- AMDのオリジナルのK9とK10プロジェクトはキャンセル

- インテルのコアマイクロプロセッサベースのプロセッサに対して、性能面での優位性を示すことが、AMDの死活問題となる

- 多くのベンダーがAMDを採用しているが、逆に言えば、 非常に厳しい要求がある

- プロセッサの製造コスト、コミットできる出荷ボリューム、出荷時期

- 単にベンチマークの性能だけでなく、製品としての評価が重要

- インテルの製品プラン、製品出荷、ボリュームへの対抗

- 非常に明確なインテルのプランとデモの実施

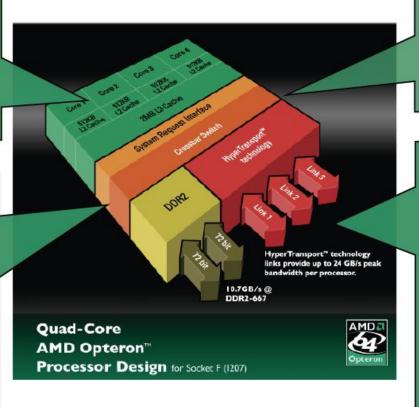

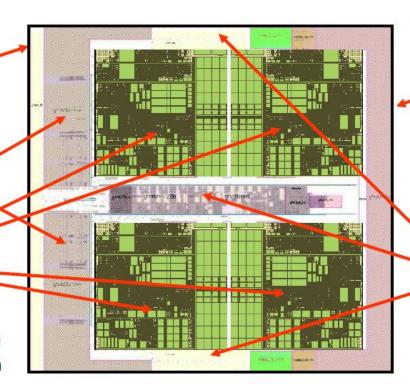

#### **AMD Barcelona**

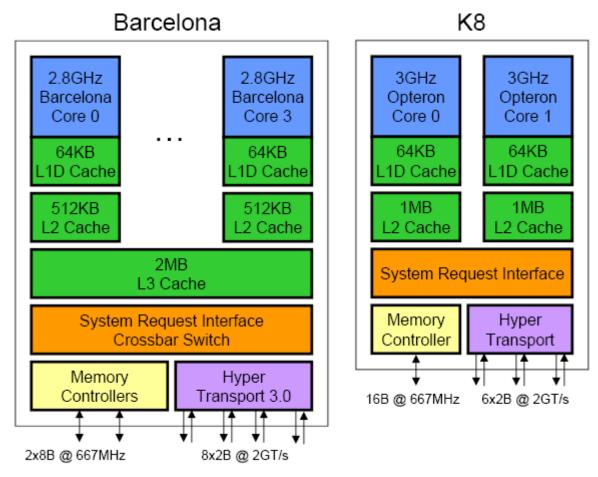

- ・プロセッサデザイン

- 4つのコアがそれぞれキャッシュを持ち(2x32K K1、 512K L2) 共有のL3キャッシュ(2MB)を介して通信 を行う

- DRAMとHyperTransportのための内部スイッチへのL2からのポートは一本

- プロセッサ内部のコアのスケーラビリティは高いが、 プロセッサ構造は非常に複雑になり、また、プロセッサのダイサイズが非常に大きくなっている

- プロセッサクロックの向上が困難であり、製造時の歩留まりの問題が発生する

- ・プロセッサの消費電力を低くすることが難しい

# Inside Barcelona: AMD's Next Generation\_\_\_\_

.....However, the current socket infrastructure only supports three HT1.1 lanes, so these innovative system designs will have to wait for a new socket interface. Initially, each link will run at 2GT/s, ••••••

http://www.realworldtech.com/page.cfm?ArticleID=RWT051607033728

# ネットワーク上の評価レポート

- Inside Barcelona: AMD's Next Generation

- http://www.realworldtech.com/index.cfm

- 詳細なAMD Barcelonaに関する技術解説

- Computex 2007: AMD's Barcelona and Other Products

- http://www.anandtech.com/

- Computex 2007 でのAMDのデモの状況の説明

- "In the end, performance was absolutely terrible. We're beginning to understand why AMD didn't let us test Barcelona last month. It's not that AMD is waiting to surprise Intel; it's that the platform just isn't ready for production yet."

# Introducing "Barcelona"... Native quad-core upgrade for 2007

#### Native Quad-Core Processor

To increase performance-per-watt efficiencies <u>using the same Thermal</u> **Design Power.**

#### Advanced Process Technology

#### 65nm Silicon-on Insulator Process

Fast transistors with low power leakage to reduce power and heat.

#### Platform Compatibility

Socket and thermal compatible with "Socket F"

# Direct Connect Architecture

- Integrated memory controller designed for reduced memory latency and increased performance

- Memory directly connected

- Provides <u>fast CPU-to-CPU</u> <u>communication</u>

- CPUs directly connected

#### AMD's Next Generation Processor AMD **Technology**

Native quad core die

Expandable shared 13 cache

IPC enhanced CPU cores

- 32B instruction fetch

- Improved branch prediction

- Out-of-order load execution

- ▶ Up to 4 DP FLOPS/cycle

- ▶ Dual 128-bit SSE dataflow

- Dual 128-bit loads per cycle

- Instruction Extensions

- Power Management Extensions

Optimized for 65nm SOI and beyond

**Enhanced Direct** Connect Architecture and Northbridge

- Enhanced HyperTransport<sup>™</sup> links

- Enhanced crossbar

- ▶ DDR2 with migration path to DDR3

- Enhanced power management and RAS

#### **AMD Barcelona**

- AMDの65nmプロセスによる最初のクァッドコア、 シングルダイ、x86プロセッサ

- クァッドコア間の通信の最適化

- 非常に多くのトランジスタを搭載(インテルの次期プロセッサの2倍)した、非常に大型のプロセッサ

- 製品プラン(2ソケットワークステーション、サーバを2007年の第3四半期以降、4ソケットは??)

#### 性能

- 浮動小数点演算性能を2倍、整数演算性能の向上は限定的(3命令実行/サイクル、インテルは、4命令実行/サイクル)

- メモリコントローラの性能は30%向上

- HyperTransport(HT)リンクの性能向上

#### AMD Barcelona - 期待

- 浮動小数点演算性能 HPC アプリケーション性能

- インテルがコアマイクロアーキテクチャを発表する以前の5年間は、常にAMDがx86アーキテクチャでは優位性を示す

- AMDの多くの 'マーケティング' は、この分野での成功に依存している

- 再度、インテルのクァッドコアに対して、少なくとも30%以上の性能面での優位性を示すことがAMDには必要

- 汎用用途での性能

- 整数演算性能は、汎用用途では非常に重要であり、将来の モバイル用途では非常に重要

- AMD Barcelonaでの整数演算性能の向上

- メモリ性能とSMPスケーラビリティ

- HyperTransportの性能向上による4ソケット以上の構成での性能向上

- コア間での直接通信とメモリバンド幅

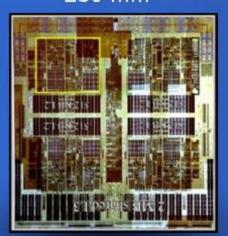

#### **Die Size Matters**

High-Performance Quad-Core Processors in Manufacturable Dual-Die Implementation

AMD Barcelona 65nm 463m Transistors<sup>1</sup> 4 MB Cache<sup>1</sup>

143 mm<sup>22</sup> 143 mm<sup>22</sup>

Intel® Xeon® (Clovertown)

65nm

681m Transistors

8 MB Cache

107 mm<sup>22</sup> 107 mm<sup>22</sup>

Penryn Quad Core Server 45nm Hi-k 820m Transistors 12 MB Cache

# Penryn – インテルの2007ターゲット

- 現在のCore2/Xeonプロセッサの45nmプロセスでの製造

- トランジスタは20%高速

- 20%以上のクロックアップでも、消費電力は現在のプロセッサよりも低い

- 非常に小さなダイサイズ(107平方ミリメータ、410トランジスタ)

- 全マーケットセグメントでの製品化

- サーバ、ワークステーション、ハイエンドPC向け(2007年第4四半期) モバイル向け(2008年第1四半期)

- 既に多くのデモ、サンプルを出荷

- シングルダイ(デュアルコア)、デュアルダイ(クァッドコア)を同時に製品化(Wolfdale-DC、Yorkfield-QC、Harpertown-QC(4ソケット)

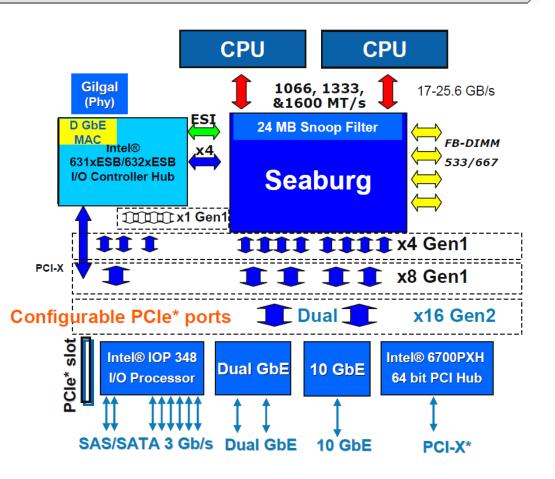

- 既に、Penryn向けプラットフォームを出荷

- P35とP38(ハイエンドディスクトップ)

- Stoakley (Seaburg チップセット) (2ソケットサーバ、ワークステーション)

- Caneland (4ソケットサーバ)

- Santa Rosa (モバイル)

# Penryn向けプラットフォーム

**CPU CPU** DIB ESI San Clemente ICH9R **MCH** PCI Express\* lanes Configurable set of PCI Express\* ports 10P 348 Dual GbE SAS/SATAII PCI-X\*

デュアルプロセッサ対応の上位プラットフォームとなるStoakleyプラットフォーム: FB-DIMMのサポート、エンタープライズ向けICHのサポートなど、Bensleyプラットフォームの直系

デュアルプロセッサ対応の下位プラットフォームとなるCranberry Lake: 熱とコストの両面で有利なDDR2メモリをサポートするほか、ICHもクライアント向けチップセットと共通のICH9Rを用いる。

#### Penryn Family Optimized Microarchitecture

Intel SSE4 instructions Fast Super Shuffle Engine

Fast Radix-16 Divider Enhanced Intel Virtualization Technology

Larger Caches: 6MB, 12MB 24-way Set Associativity

Split Load Cache Enhancement Higher Bus Speeds

Deep Power Down Technology Enhanced Intel Dynamic Acceleration Tech > 3 GHz

Increased

Performance and

Energy Efficiency

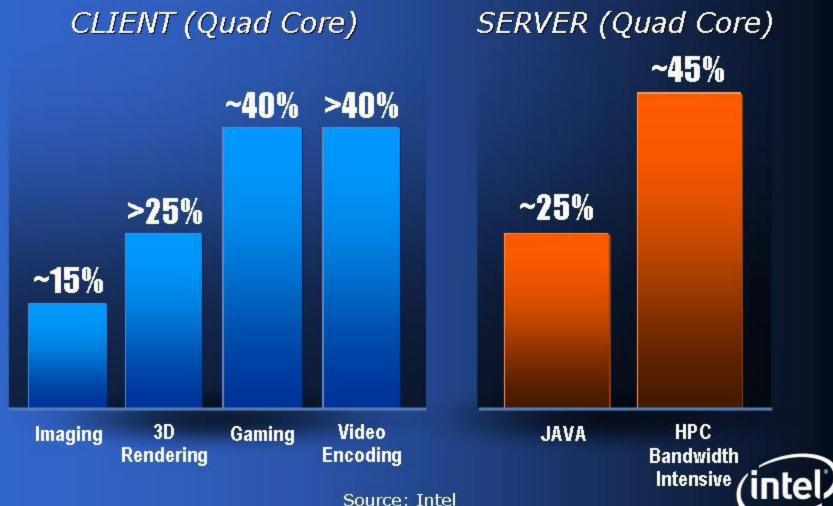

# Penryn Family Performance **Early Indicators**

45nm High-k vs. 65nm Intel® Core™ 2 and Xeon™ Processors

# Penryn 機能強化と性能

- 機能強化ポイント(浮動小数点演算性能、メモリ性能、仮想化)

- SSE4命令、除算演算、Super Shuffle Engine

- 浮動小数点演算性能を最大で2倍(マルチメディア)

- L2キャッシュサイズの増加(50%アップ、各デュアルコアあたり6MB)とアクセススピードの向上

- クロックアップ

- 3.33GHz/FSB 1333 (デスクトップ)、3.2GHz/FSB 1600 (サーバ)

- 2008年第2四半期には、3.6-3.8GHzのサポート(予測)

- デュアルコアとクァッドコア(デュアルダイ)で同じ動作クロックをサポート

- 既にベンチマーク性能を公開

- ベンチマーク結果としては、現在のプロセッサに対して、20%-50%の性能向上

- クロック性能以上の性能向上

- エンタープライズ、HPC(技術計算)、ゲームの各分野全てにおいて、高い性能

- SSE4の最適化が進めばさらに高い性能の実現も可能

# 競合 – シナリオ

- 1. Barcelonaが2.5GHz(4コア)で、Penrynが、3.33GHz(4コア)で、それぞれがコミットした性能を発揮すると仮定した場合

- 一般的なアプリケーションでは、Penrynが、20%-40%の性能面での優位性 を持つ

- 浮動小数点演算(技術計算、マルチメディア、ゲーム)などでも、Penrynが0-20%の性能面の優位性を持つ

- メモリ性能が重要なアプリケーションでは、Barcelonaが0-20%の性能面の優 位性を持つ

- 2. Barcelonaが~2.7GHz(4コア)で、Penrynが、3.33GHz(4コア)で、それぞれがコミットした性能を発揮すると仮定した場合

- 一般的なアプリケーションでは、BarcelonaとPenrynの性能差は、狭まり、浮動小数点演算(技術計算、マルチメディア、ゲーム)や、メモリ性能が重要なア プリケーションでは、Barcelona性能面の優位性を持つ

- 3. Barcelonaが2.5GHz(4コア)で、Penrynが、3.6GHz(4コア)で、それぞれ がコミットした性能を発揮すると仮定した場合

- 一般的なアプリケーションでも浮動小数点演算(技術計算、マルチメディア、 ゲーム)や、メモリ性能が重要なアプリケーションでも、Penryn性能面の優位 性を持つ

- さらにFSBの高速化によって、性能差は更に大きくなる

#### インテル / AMD CPU 2007. 11

AMDは、シングルダイあたり、2倍のコアを搭載し、コア間の高速インターコネクトをもつ。インテルは、より高速のクロックと大きな共有キャッシュを持つ。FSBとメモリの性能も改善。

# プロセッサ比較一覧

|                     | 65nm<br>Intel Core<br>Microarchitecture                        | 45nm Hi-k<br>Penryn                                                 | AMD K8                                             | Barcelona                                             |

|---------------------|----------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------|

| Production Date     | 1H 2006                                                        | 2H 2007                                                             | 2003                                               | 2H 2007                                               |

| Clock Frequency     | 3GHz                                                           | Up to >3GHz<br>Demo'd 3.33GHz                                       | 3GHz                                               | >2GHz<br>Demo'd 1.8GHz?                               |

| Technology          | Intel 65nm                                                     | Intel 45nm Hi-K<br>+Metal Gate                                      | 90nm/65nm                                          | 65nm                                                  |

| Cache               | Shared L2<br>Higher BW<br>256bit data width                    | 24 way Shared L2<br>Higher BW<br>256bit data width                  | Dedicated L2<br>64bit data width                   | Shared L3<br>128 bit data width                       |

| Toatal L2/L3 Cache  | Up to 8MB                                                      | Up to 12MB                                                          | Up to 2MB                                          | Up to 4MB                                             |

| Memory Access       | Improved Prefetch 3 Pre-fetchers Memory Disambiguation DDR-2/3 | Decreased Latency 3 Pre-fetchers Memory Disambiguation DDR-2/3      | Integ. Mem. Controller<br>2 Pre-fetchers DDR-<br>2 | Integ. Mem.<br>Controller 2 Pre-<br>fetchers<br>DDR-2 |

| Issue Width         | 4 Issue                                                        | 4 Issue                                                             | 3 Issue                                            | 3 Issue                                               |

| Pipeline Efficiency | 14 Stage Speculative OOO Loads/Stores Macro & Micro Fusion     | 14 Stage<br>Speculative OOO<br>Loads/Stores<br>Macro & Micro Fusion | 12 Stage<br>No load/store re-<br>ordering          | 12 Stage<br>No load/store re-<br>ordering             |

| Sytem Bus           | Up to 1333MHz                                                  | Up to 1600MHZ                                                       | 1000MHz                                            | 1000MHz                                               |

| SSE                 | Intel SSE3 ISA<br>128 Bits/Cycle                               | Intel SSE4 ISA<br>128 Bits/Cycle                                    | SSE3(Equiv)<br>64 Bits/Cycle                       | SSE3(Equiv)<br>128 Bits/Cycle                         |

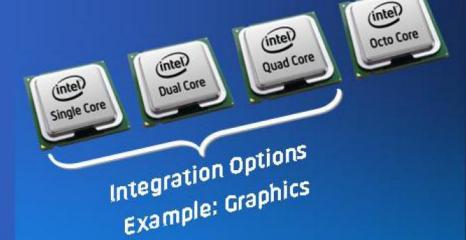

# Nehalem - 次世代マイクロプロセッサ

- 次世代CPUマイクロアーキテクチャ Core3?

- ベースは、現在のCore2となるが、マイクロアーキテクチャを大きく変更

- HyperThreadingをSMTとして再実装

- CSIインターコネクトの導入 (AMDのHyperTransportと同様機能+α)

- Beckton(4 CSIとマイクロバッファメモリ) とGainestown(3CSIと3xDDR3メモリ)

- 4コア/シングルダイ、8コア/デュアルダイ

- より高い動作周波数(4GHz以上?)

- チップセット: Stoutland(4ソケット)、Tylersburf(2ソケット)、TBD(ソケット)

- SMT:Simultanout Multithreading

- 従来のHyperThreadの欠点の克服

- スレッドアプリケーションでの性能向上

- 16スレッド(デュアルダイ、8コアチップ)

- CSI: Coherent Scalable Interface 近辺にCPU、IO、アクセレータデバイスを直接接続

- HyperTransport 3以上の性能を目標

- Nehalemは、プロセッサにメモリコントローラを内蔵

- DDR3 3+メモリチャンネルのサポート

#### Nehalem

#### Dynamic Scalability for Efficient Performance on Demand

Fully Unlocks Intel 45 nm High-k Silicon Benefits

Leverages 4 Issue Intel® Core™ Microarchitecture Technology Dynamically Managed Coresi Threadsi Caches Simultaneous Multithreading Multi-level Shared Cache Architecture Performance Enhanced Dynamic Power Management

#### **Design Scalability Optimizes for Each Market Segment**

New System Architecture Scalable &

Configurable

Cache,

Interconnects &

Memory

Controllers

Optional High Performance Integrated Graphics For Client Scalable

Performance:

1 to 16+

Threads &

1 to 8+ Cores

Initial Products in Production in '08

# The Magic of 45 nm (Spectrum of Intel Architecture)

SYSTEM ON A CHIP

Ultra-low Cost and Power Optimized Architecture

Notebook, Desktop and Server

Intel® Core™ 2 and Nehalem Architecture

**POWER**

Source: Intel Internal

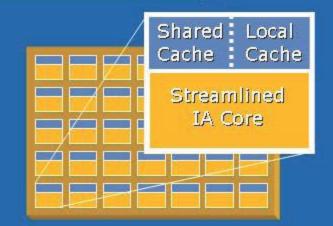

# What the Cores will look like: From a few large cores to many lightweight cores

Optimized for speed

Optimized for performance/watt

Cache

**Pentium**

Pentium era chips

optimized for raw

speed on single

threads.

Pipelined, out of order

execution.

Today's chips use cores which balance single threaded and multi-threaded performance

5-10 years: 10s-100s of energy efficient, IA cores optimized for multithreading

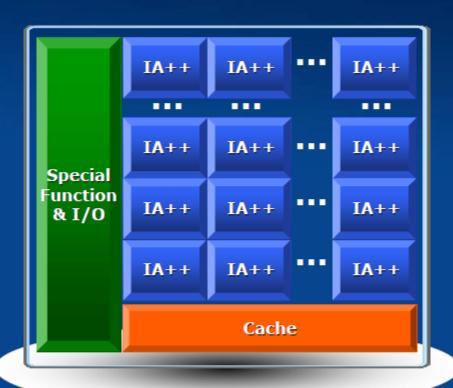

#### Bringing IA Programmability and Parallelism to High Throughput Computing

- Highly parallel, IA programmable architecture in development

- Ease of scaling for software ecosystem

- Array of enhanced IA cores

- Scientific Computing, RMS,

Visualization, Financial

Analytics & Health applications

- Teraflops of performance

# Intelが進める、32コアCPU「Larrabee」

- Intelは、メニイコア(Many-core)CPUの第1弾「Larrabee(ララビー)」の製品化に向けて進んでいる。Intelでは、数十個規模のCPUコアを載せたマルチコアCPUをメニイコアと呼んでいる。Larrabeeは"ハイスループットコンピューティング"向けに特化した、IA(Intel Architecture)プロセッサで、多数のCPUコアで並列処理を行なう。

- 「Larrabeeが登場したら、ハイパフォーマンスコンピューティングのベンチマークを総なめにする可能性がある」とある業界関係者は期待を語る。

- Larrabeeのターゲットアプリケーションは、一目見てわかる通り、GPUがGPGPU(またはGPUコンピューティング)でターゲットにし始めている領域と完全に重なる。つまり、LarrabeeはIntelによるGPGPUの動きに対する回答だ。IntelとGPUベンダーは、ハイパフォーマンスな浮動小数点演算性能が必要な並列コンピューティングの領域で、真っ向からぶつかることになる。

- http://pc.watch.impress.co.jp/docs/2007/0611/kaigai364.htm

#### Timelines 2007 - 2008

- Intel Penryn 製品発表(予想)2007年9月 (IDF)、ボリューム出荷(予想)11月

- 2ソケット、1ソケット製品を最初に製品化

- 2ソケット、1ソケット向けクロックアップ版を2008年4 月に製品化(予想)

- 4ソケットは、2008年5月までに製品化?

- AMD Barcelona プレスへの説明(5月)、製品発表(8月)、ボリューム製品出荷(9月)?

- 製品開発に関する遅れの噂

#### AMDのクアッドコア「Barcelona」に出荷遅延のうわさ

| <ul><li> ● AMDのクアッドコア「Barcelona」に出荷遅延のうわさ──3カ月遅れの10月に?:プラットフォーム - Computerworld.jp - Mo □ □ ※</li></ul> |  |  |  |  |

|---------------------------------------------------------------------------------------------------------|--|--|--|--|

| ファイル(E) 編集(E) 表示(Y) 履歴(S) ブックマーク(B) ツール(T) ヘルプ(H)                                                       |  |  |  |  |

|                                                                                                         |  |  |  |  |

| ♣ Firefox を使ってみよう Q 最新ニュース                                                                              |  |  |  |  |

| Google - amd barcelona 遅れ ▼ ↓ G 検索 - 参 🎳 チェック - 🗋 登録 - 🔁 オプション 🤌 🔘 amd 🔘 barcelona 🔘 遅れ                 |  |  |  |  |

| ©W AMDのクアッドコア「Barcelona ☑ ◯W AMDのクアッドコア「Barcelon ☑ ▼                                                    |  |  |  |  |

| COMPUTERWORLD IDG Japan Webmedia                                                                        |  |  |  |  |

| http://www.computerworld.jp/news/plf/66529.html                                                         |  |  |  |  |

| ブラットフォーム                                                                                                |  |  |  |  |

| 「米国」<br>AMDのクアッドコア「Barcelona」に出荷遅延のうわさ――3カ月遅れの10月に?<br>同社は「開発は予定どおり」と火消しに躍起                             |  |  |  |  |

(2007年06月07日)

サーバ向けクアッドコアOpteron(開発コード名: Barcelona)の出荷時期を巡り、米国AMDがうわさの火消しに躍起になっている。 同プロセッサの出荷時期はこれまで7月と見られていたが、10月にずれ込む可能性が取りざたされているのだ。仮に出荷が遅れ るとなると、同プロセッサを対インテル戦略の中心に据えたAMDの計画は後退を余儀なくされることになる。

一般に、サーバ向けのプロセッサは、デスクトップPCやノートPC向けよりも利幅が大きい。そのため、Barcelonaプロセッサの出 荷襗延は、AMDの今年の収益に悪影響を及ぼすと見られている。シティグループのアナリスト、グレン・ヤング氏が6月5日に公表 したリポートによると、同プロセッサの出荷が遅れた場合、AMDの赤字は1株当たり2ドル48セントから2ドル59セントに拡大すると いう。

ヤング氏は同リポートの中で、「AMDICとって、Barcelonalはサーバ向けプロセッサの シェアをインテルに奪われつつある状況に歯止めをかける最大のチャンスと見られてい た。AMDは先ごろ東芝からノートPC用プロセッサを受注しており、これで売上高に対す る否定的な影響は相殺されると思われるが、それでもBarcelonaの出荷遅延は総利益 にマイナスの影響を与えるはずだ」と述べている。

トムソン・フィナンシャルの 予測によると、 今年度の AMDは1 株当たり2ドル47セントの 赤字を計上する見通しだが、ヤング氏は同社の赤字額がさらに増えると見ている。

AMDは数カ月前から、Barcelonaプロセッサを今年下半期に出荷し、インテルとの 価 格戦争で受けたダメージから立ち直ると明言していただけに、今回のうわさはタイミン グが悪かった。同社は、今年1月の2006会計年度第4四半期決算で5億7400万ドルの 赤字だったのに続き、今年4月の2007会計年度第1四半期決算でも6億1,100万ドルの 赤字を計上している。

AMDのCEOであるヘクター・ルイス氏は、5月3日に開催された年次株主総会の場 で、Barcelonaプロセッサこそ財政面の重荷を取り去ってくれる重要な製品であると確 調。インテルがチップ製造能力を強化してきても、AMDは革新的な設計で競争力を維 持できると語った。

AMDは6月6日、台湾で開催された展示会「Computex」でBarcelonaプロセッサのデモ が行われたことを証拠に、開発が予定どおり進んでいると力説した。このデモとは、同プ

ロセッサの試作品を搭載した各社(スーパーマイクロ・コンピュータやタイヤン・コンピュータ、ユニワイド・テクノロジーズ)のサーバ によるものを指している。

タイヤン・コンピュータによるBarcelonaプロセッサ搭載 サーバのデモ

www.computerworld.jp 🖴

🥹 http://japan.cnet.com - AMD、「Budapest」の遅れは認めるも「Barcelona」は予定通りに出荷... 🕒 😐 📗

ファイル( $\underline{F}$ ) 編集( $\underline{F}$ ) 表示( $\underline{V}$ ) 履歴( $\underline{S}$ ) ブックマーク( $\underline{B}$ ) ツール( $\underline{T}$ ) ヘルプ( $\underline{H}$ )

掲載日時: 2007/06/06 18:14

AMD、「Budapest」の遅れは認めるも「Barcelona」は予定 iapan.cuel.com 通りに出荷と説明

AMDの4コアプロセッサ「Barcelonalのスケジュールが遅れているという見方が出始めたが、AMDは これを否定する見解を示した。ただし、クレイのスパコンに搭載予定の類似ブロセッサ「Budapest」に ついては出荷遅れを認めている。

筆者など:文:Stephen Shankland(CNET News.com) 翻訳校正:緒方亮、長谷睦

チャネル名:ニュース:情報システム

URL: http://japan.onet.com/news/ent/story/0,2000056022,20350301,00.htm

CitigroupのアナリストGlen Yeung氏の指摘をきっかけとして、Advanced Micro Devices (AMD)のクアッドコア(4コア)プロセッサ「Barcelona I (開発コード名)のスケジュールが遅れて いるという見方が出始めた。だが、AMDは米国時間6月5日、スケジュールは予定通りに進ん でいると説明した。しかし、スーパーコンピュータメーカーCrayに供給されるBarcelonaと近いタ イブのブロセッサ「Budapest」(開発コード名)の出荷は、スケジュールから遅れているという。

5日、AMDの広報担当者Phil Hughes氏は、Barcelonaには「遅れはない」と語った。Barcelona と、同プロセッサを搭載するシステムは2007年第3四半期に出荷されるという。

Intelが投入したCore 2ベースのサーバ向けプロセッサ「Xeon I (デュアルコアは5100番台、ク アッドコア(は5300番台) (に奪われた市場シェアを取り戻したいと考えるAMD(にとって、 Barcelonaは戦略的に重要なチップだ。

だが、一方でCravへのBudapestの出荷は遅れている。「Cravに関して、Budapestの部品を Crayがいつ入手するか、という部分についてのみ、スケジュールを変更した」とAMDのHughes 氏は説明し、それ以上の詳細は明らかにしようとしなかった。

Barcelonaは2つ以上のプロセッサンケットをもつシステム向けに設計されている。一方、 Budanestは単一ソケットのシステム向けに設計されている。

Cravは5月に、AMDプロセッサをベースにしたスーパーコンピュータ「XT4」について、4コアに 対応させるアップグレードを「2007年後半」まで延期すると発表している。

この記事は海外CNET Networks発のニュースを編集部が日本向けに編集したものです。

Copyright @ CNET Networks, Inc. All Rights Reserved.

完了

完了

#### インターネットニュース

- AMD、「Budapest」の遅れは認めるも「Barcelona」は予定通りに出荷と...

- AMDの4コアプロセッサ「Barcelona」のスケジュールが遅れているという見方が出始めたが、AMDはこれを否定する見解を示した。ただし、クレイのスパコンに搭載予定の類似プロセッサ「Budapest」については出荷遅れを認めている。 japan.cnet.com/news/ent/story/0,2000056022,20350301,00.htm?ref=rss

- AMDのクアッドコア「Barcelona」に出荷遅延のうわさ――3カ月遅れの10月...

- そのため、Barcelonaプロセッサの出荷遅延は、AMDの今年の収益に悪影響を及ぼすと見られている。シティグループのアナリスト、グレン・ヤング氏が6月5日に公表したリポートによると、同プロセッサの出荷が遅れた場合、AMDの赤字は1株当たり2ドル48セント...

www.computerworld.jp/news/plf/66529.html

- Yahoo!ニュース CNET Japan AMD、「Budapest」の遅れは認めるも ...

- CitigroupのアナリストGlen Yeung氏 の指摘をきっかけとして、Advanced Micro Devices(AMD)のクアッドコア(4コア)プロセッサ「Barcelona」(開発コード名)のスケジュールが遅れているという見方が出始めた。だが、AMDは米国時間6月5日、スケジュール ... headlines.yahoo.co.jp/hl?a=20070606-00000013-cnet-sci

# AMDからのプレスリリース

#### AMD、業界初のネイティブx86クアッドコア・プロセッサを8月に 出荷開始

http://www.amd.com/jpja/Corporate/VirtualPressRoom/0,,51\_104\_543~118194,00.html

#### 要約すると・・・・

- 米AMDは6月29日、クアッドコアOpteronプロセッサ(コードネーム「Barcelona」)をパートナー企業向けに8月に出荷開始すると発表した。搭載システムの出荷は9月となる見通し。

- 8月に出荷開始となるのは、クロックスピード最高2GHzの「低消費電力」および「標準」バージョンの製品で、一部のデータベース製品では最高70%、浮動小数点演算では最高40%の性能向上を実現できるという。

- 第4四半期(10~12月期)には、より高速の「標準」および「スペシャルエディション」バージョンを投入予定だとしている。

# 今回の発表について・・・WSJ

- http://it.nikkei.co.jp/business/news/index.aspx?n=RSBQV5885%2002072007

- AMDが新製品発売予定発表、インテルへの反撃効果弱まる可能性【WSJ】 ニューヨーク(ウォール・ストリート・ジャーナル)米半導体大手のアドバンスト・マイクロ・デバイシズ(NYSE: AMD)が6月29日、待望の半導体新製品であるクアッドコアのマイクロプロセッサー「オプテロン」(開発名バルセロナ)の発売計画を発表した。これによると、半導体最大手の米インテル(Nasdaq: INTC)への効果的な反撃が遅れ、成功する確率が低くなるかもしれない。

- AMDの発表によると、コンピューターメーカーへの出荷開始は8月で、当初バージョンの動作周波数は最大2ギガヘルツ。この製品を搭載したシステムの出荷は9月になる。

- AMDはこれまで、バルセロナについて、コンピューターの性能を左右する重要な要素である動作周波数を明らかにしていなかった。同社のサーバー・ワークステーション部門担当副社長のランディ・アレン氏は、「一部の業界関係者は2.7 ギガヘルツから2.8ギガヘルツの製品を発売すると予想していた」と認めた。一部のアナリストは、新製品を搭載したシステムの出荷は9月より早い時期を予想していたが、AMDは「新製品の出荷は2007年半ば」としか明らかにしていなかった。

- ・ アレン氏によると、当初バージョンの発売後間もなく、それより動作周波数の高いバージョンを発売するという。だが米情報技術(IT)市場調査会社インスタットのアナリスト、ジム・マクレガー氏は、AMDの発表について「落胆する内容だった。当初発売する新製品は、インテルの現行製品に比べ顕著に優れた性能を備えたものにはなりそうもない。また、高性能バージョンの出荷が遅くなると、インテルが07年後半から08年にかけて発売予定の改良型新製品と競争することになる」と指摘した。

#### Timelines 2007 - 2008

- Nehalem:インテルの次期マイクロプロセッサ

- 2008年第4四半期をターゲット

- 製品発表、製品化は、Core2やPenrynと同様のプロセスとなる

- 32nm "Westmere" プロセスによる製品化は、 2009年第4四半期をターゲット

- AMD Shanghai: 45nm版 Barcelona (2009年中頃)

- デュアルダイパッケージの採用(8コア)

- ダイ間は、HT3で接続

- 4コアダイあたり6MB L3 キャッシュ

#### 予想

- 2008年前半: Penryn .vs. Barcelona

- 各プロセッサの出来次第(3つのシナリオ)

- 2008年末: Nehalem .vs. Barcelona

- Nehalemが仕様どうりであれば、Nehalemが性能 面での優位性が非常に高い

- Nehalemは、CSIの導入という大きなシステムの変更を問題なく実現できるかどうかで、その成否が決まる

- 2009年前半: Nehalem .vs. AMD Shanghai

## まとめとして

- 各社プロセッサの出荷時期

- インテルの次期45nmプロセッサ「Penryn」(開発コード名)今年の第3四半期末か第4四半期はじめに出荷

- AMDのサーバ向けクアッドコア(開発コード名: Barcelona)の出荷時期は8月以降?

- 現状のBarcelonaの状況は非常に厳しい

- 出荷が年末から来年初めになった場合、ネィテイブ クアッドコアとしての利点での優位性を失う

- 動作クロックが2.5GHz以下の場合も同様に優位性 を失う

## まとめとして

- AMD「Barcelona」の状況

- 2年前のインテル「Montecito」の悪夢がAMDに… 状況は非常に似ている:

大型のHPC案件の受注と納期のコミット 納入遅れによるOEMの苦境→クレイが業績見通しを 下方修正

競合 – シナリオ (3)の可能性

## この資料について

ここに掲載した資料は、弊社の調査と見解に基くものであり、資料の中で示されている製品やサービスを提供している各社の公式な見解でも、また、マーケティング戦略に基くものではありません。あくまで、弊社としての意見だということにご注意ください。これらの資料の無断での引用、転載を禁じます。社名、製品名などは、一般に各社の商標または登録商標です。なお、本文中では、特に®、TMマークは明記しておりません。

In general, the name of the company and the product name, etc. are the trademarks or, registered trademarks of each company.

Copyright Scalable Systems Co., Ltd., 2007. Unauthorized use is strictly forbidden.

2007年7月3日

# さらに詳しい情報や最新情報は.....

ホームページにて公開しています。 ホームページには、お問い合わせ窓 口も開設してありますので、ご利用く ださい。

コンサルテーション

http://www.sstc.co.jp

製品技術

http://www.hp2c.biz

2007年6月11日